Motivado pelos avanços em microeletrônica e uma abordagem holística, nós da Fraunhofer IIS/EAS seguimos dedicados ao desenvolvimento de novos produtos eletrônicos

conceitos de design e fechamento de lacunas no fluxo de projeto.

A crescente miniaturização da eletrônica, novas tecnologias de fabricação e a crescente gama de funções coloca exigências especiais sobre o seu desempenho e o processo de projeto. Nosso trabalho é, portanto, focado em atender à crescente complexidade de circuitos com novos conceitos de design. Nosso objetivo é uma rápida economia de recursos, livre de erros e desenvolvimento seguro de sistemas eletrônicos.

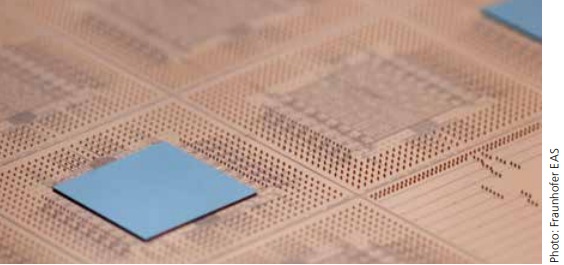

Mas também novas tecnologias como chiplets estão em nosso foco sob o aspecto “Mais do que Moore”. O suporte no processo de design também é fornecido pelo “IP Inteligente” – a automação solução para analógico e misto analógico/digital projeto de chip. Estruturação sistemática e automação de tecnologia cruzada significativamente acelerar o processo de desenvolvimento.

A reutilização é melhorada e os recursos são conservado. Testando sistemas complexos inteiramente sem o uso de recursos de hardware pode ser implementado com um Deep SiL individual metodologia. Nesse processo, o comportamento do hardware é mapeado com a mesma precisão conforme necessário de forma absolutamente virtual. Isso aumenta a cobertura do teste e melhora a robustez do sistema. Ao mesmo tempo, o desenvolvimento ágil processos são criados e a economia risco é significativamente reduzido.

Andy Heinig

Fraunhofer IIS/EAS

andy.heinig@eas.iis.fraunhofer.de

Considere: há inúmeras limitações. Sugira apontando